#### **GENERAL DESCRIPTION**

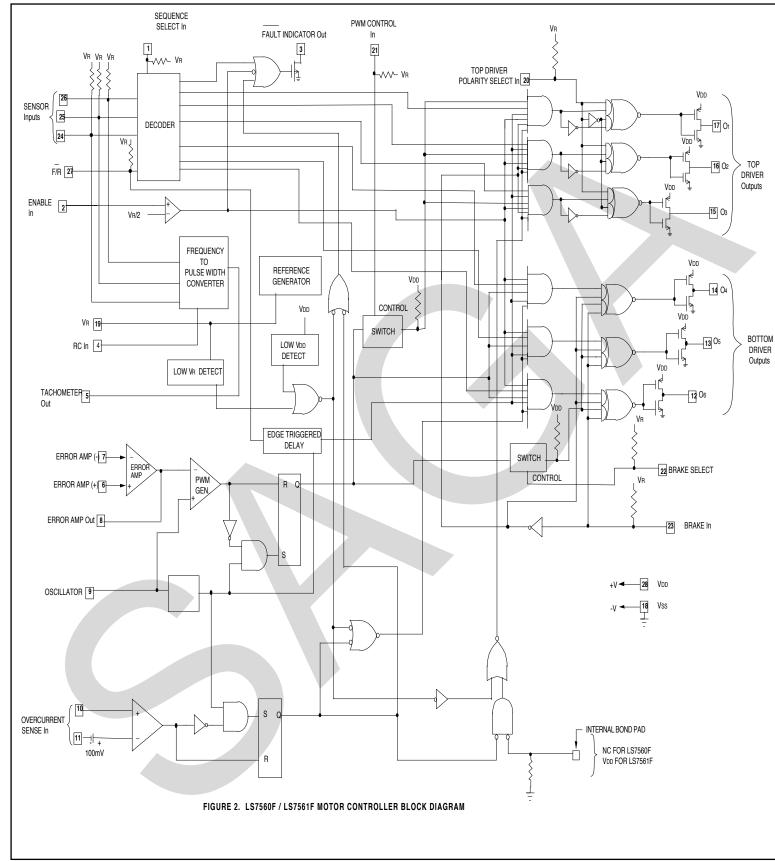

The LS7560F/LS7561F are designed to control three or four phase brushless DC motors in a closed or open loop configuration. The IC consists of a decoder which provides proper commutation sequencing, a frequency-to-pulse width converter and error amplifier for closed loop motor speed control, a PWM comparator and sawtooth oscillator for external driver power control and a 6V reference generator for supplying power to motor sensors. Also included is Fault detection and indication, overcurrent sensing, dynamic motor braking, forward/ reverse input, sensor spacing selections and an enable input control. The overcurrent sense condition will disable all output drivers when using the LS7560F and only the bottom drivers when using the LS7561F.

The IC operates from 10V to 18V and provides CMOS compatible outputs for interfacing with external power devices. Operating below 10V will activate a Fault Indication Output and disable all Output Drivers.

#### INPUT/OUTPUT DESCRIPTION: (See Figure 2)

#### SEQUENCE SELECT Input (Pin 1)

A High on this input selects  $60^{\circ}/300^{\circ}$  and a Low selects  $120^{\circ}/240^{\circ}$  electrical sensor separation. Use of a 300° or 240° motor will cause opposite direction rotation as compared to a  $60^{\circ}$  or  $120^{\circ}$  motor.

### F/R Input (Pin 27)

A High on this input selects Forward direction and a Low selects Reverse direction. The motor drive outputs are disabled for 2 clock cycles at the onset of a direction change.

#### S1, S2, S3 Inputs (Pins 24, 25, 26)

Hall Sensor inputs which are decoded to determine the Motor Commutation Sequence. An invalid input code disables all motor outputs. Inputs have Schmitt Trigger buffers for noise immunity.

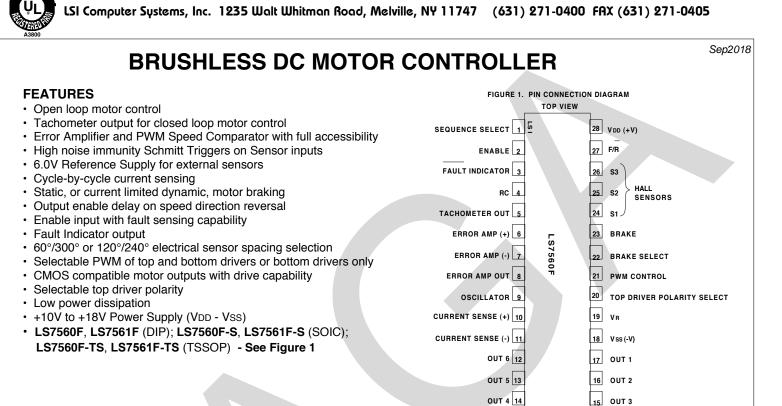

**LS7560F**

LS7561F

#### BRAKE Input (Pin 23)

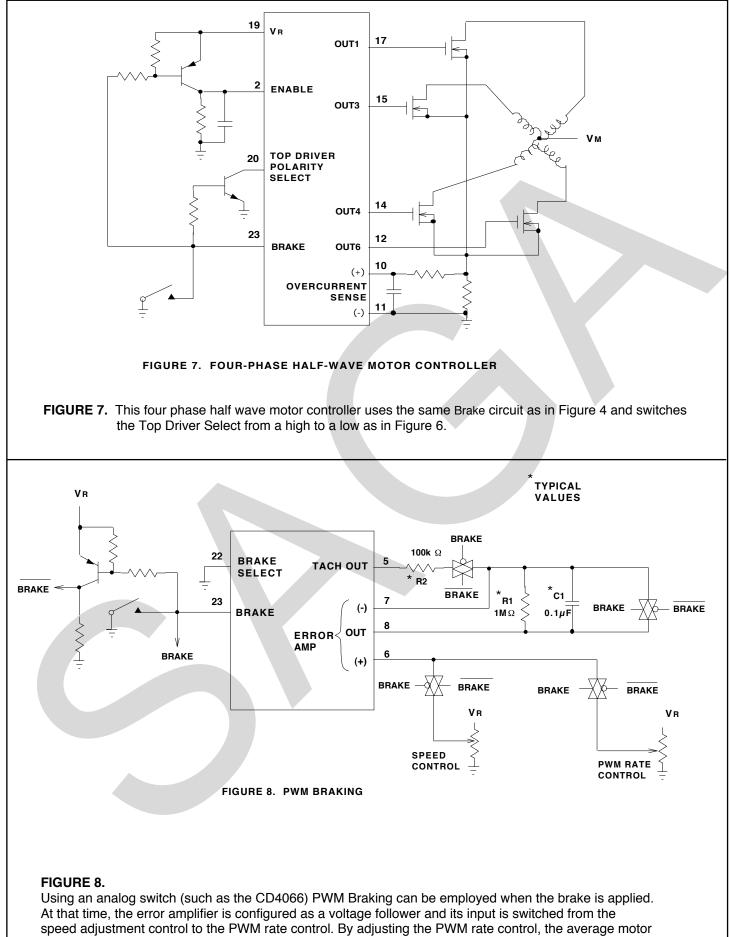

With the Brake Select input Low, a High on the Brake input forces the Top Drivers to an Off condition and the Bottom Drivers to a PWM On condition. If the Motor is under Closed Loop control, the Loop must be opened and the error amplifier output connected to the Error Amp (-) input. By controlling the voltage at the Error Amp (+) input, the PWM duty cycle is controlled during braking (see Figure 8). This manner of braking prevents the Bottom Motor Drivers from drawing excessive current, a condition which can occur during normal braking, when the Bottom Drivers are turned ON unconditionally. With the Brake Select input High, a High on the Brake input unconditionally causes the Top Drivers to turn Off and the Bottom Drivers to turn On. The Brake function has priority over all other functions.

#### BRAKE SELECT Input (Pin 22)

A Low on this input selects PWM control of braking and a High selects unconditional braking.

#### ENABLE Input (Pin 2)

When the Enable input is above VR/2, all Output Drivers are enabled and when it is below VR/2.2, all Output Drivers are disabled. This input has a nominal hysteresis of 0.05VR, where VR is the internally generated Reference Voltage available on Pin 19. Because the Enable input is level sensitive, it can easily be used to control operation of the IC based on an Analog Fault Condition.

## OSCILLATOR (Pin 9)

An external RC network is connected to this input to set the frequency of the Sawtooth Schmitt Trigger Oscillator. The Sawtooth is applied to the PWM Comparator along with the output of the Error Amplifier. The output of the PWM Comparator is a Pulse Width Modulated Signal which is used to vary the effective drive to the motor and, hence, the motor speed.

#### **OVERCURRENT SENSE** (Pins 10, 11)

The input to Pin 10 comes from the high side of a fractional ohm current sensing resistor. The voltage at this input is compared to an internal 100mV Reference. When the voltage exceeds the 100mV Reference, an Overcurrent Condition exists and the Output Drivers are switched Off until the end of the sawtooth oscillator ramp-up. When the sawtooth switches low, the Overcurrent Condition is sampled, and if it no longer exists, the Output Drivers are switched On again. Otherwise, the Output Drivers remain Off until the end of the next sawtooth. The input to Pin 11 comes from the low side (Gnd) of the current sensing resistor and connects to the low side of the internal 100mV Reference.

### PWM CONTROL Input (Pin 21)

A High on this input causes only the Bottom Drivers to be Pulse Width Modulated. A Low on this input causes both Top and Bottom Drivers to have PWM.

### TACHOMETER Output (Pin 5)

The output of the Frequency To Pulse Width Converter is tied to this pin. The Converter uses the three Sensor Inputs and external RC Network to generate a variable frequency output with a fixed positive pulse width.

#### RC Input (Pin 4)

The external RC network connected to this input programs the positive pulse width of the Frequency to Pulse Width Converter.

Vss (Pin 18) Supply Voltage negative terminal.

## ERROR AMPLIFIER Inputs (Pins 6, 7) Output (Pin 8)

For closed loop control, the Tachometer Output is applied through a resistor to the negative input of the Error Amplifier on Pin 7. A speed control potentiometer is connected to the positive input of the Error Amplifier on Pin 6. A parallel RC Network is connected between the Output of the Error Amplifier on Pin 8 and Pin 7. The Amplifier, configured this way, enables the variable pulse width to be converted to a DC voltage which is used to control the motor speed. The potentiometer is used to set the desired motor speed. For open loop control, configure the Error Amplifier as a voltage follower by connecting Pin 7 directly to Pin 8 and do not connect the Tachometer Output signal to the Error Amplifier.

## TOP DRIVER POLARITY SELECT Input (Pin 20)

A High on this input selects a High Polarity to enable the Top Output Motor Drivers and a Low selects a Low Polarity to enable the Top Output Motor Drivers.

## OUTPUT DRIVERS (Pins 12, 13, 14, 15, 16, 17)

Each Driver Output provides a CMOS compatible signal for driving Buffers/Power Transistors. The Outputs are capable of sinking/sourcing 25mA with a 1.5V drop across the IC, at VDD = 12V.

## FAULT INDICATOR Output (Pin 3)

Open drain output to provide sinking current for driving an external device, such as a LED, through an emitter follower (see Figure 3) to indicate a malfunction condition. The output occurs under any of the following conditions:

- 1) Overcurrent Sense condition

- 2) Enable Input below VR / 2.2

- 3) Invalid Sensor code

- 4) Chip power supply less than 9V

- 5) VR Output less than 4.1V

## VR Output (Pin 19)

6V Reference Voltage Output that can supply 20mA of current at VDD = 12V for powering input Sensors.

VDD (Pin 28) Supply Voltage positive terminal.

| MAXIMUM RATINGS (Voltages referenced to Vss) |        |                 |      |  |  |  |  |  |  |

|----------------------------------------------|--------|-----------------|------|--|--|--|--|--|--|

|                                              | SYMBOL | VALUE           | UNIT |  |  |  |  |  |  |

| Power Supply Voltage                         | Vdd    | 20              | V    |  |  |  |  |  |  |

| Voltage at any input                         | VIN    | Vss - 0.5 to VR | V    |  |  |  |  |  |  |

| Operating Temperature                        | ТА     | -25 to +85      | °C   |  |  |  |  |  |  |

| Storage Temperature                          | TSTG   | -65 to +150     | °C   |  |  |  |  |  |  |

| Output Drive Sink/Source Current             | lo     | 75              | mA   |  |  |  |  |  |  |

| VR Output Source Current                     | IR     | 30              | mA   |  |  |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12V, RT = 47k$ ,  $CT = 0.001\mu$ F, Rs = 10k,  $Cs = 0.01\mu$ F, RF = 5.6k (See Figure 3)  $TA = 25^{\circ}C$ , unless otherwise specified

| PARAMETER                                         | SYMBOL | MIN       | ТҮР     | МАХ | UNIT |

|---------------------------------------------------|--------|-----------|---------|-----|------|

| Reference Voltage                                 | VR     | 5.7       | 6.0     | 6.3 | V    |

| Line Regulation<br>VDD = 10V to 18V, IREF = 1.0mA | VR     | -         | 100     | 200 | mV   |

| Temperature Stability                             |        |           |         |     |      |

| TA = 0°C to 70°C                                  | VR     | -         | +/- 1.0 | -   | %    |

| $TA = 0^{\circ}C$ to $85^{\circ}C$                | VR     | -         | +/- 1.3 | -   | %    |

| Error Amplifier:                                  |        |           |         |     |      |

| Input Offset Voltage                              | Vio    | -         | 5       | 15  | mV   |

| Input Current                                     | lin    | -         | 0       | 10  | nA   |

| Input Common Mode Voltage Range                   | VICR   | (0 to VR) |         |     | V    |

| Open Loop Voltage Gain (RL = 15k)                 | AVOL   | 70        | 80      | -   | dB   |

| Common Mode Rejection Ratio                       | CMRR   | 60        | -       | -   | dB   |

| Power Supply Rejection Ratio                      | PSRR   | 60        | -       | -   | dB   |

|                                                   |        |           |         |     |      |

| PARAMETER                                                                     | SYMBOL   | MIN        | ТҮР        | MAX       | UNIT     |

|-------------------------------------------------------------------------------|----------|------------|------------|-----------|----------|

| Output High State ( $RL = 15k$ to Ground)                                     | Vон      | VR         | -          | -         | V        |

| Output Low State ( $RL = 15k$ to $VR$ )                                       | Vol      | -          | -          | 1.0       | V        |

| Output Source or Sink Current                                                 | lo       | -          | -          | 1.0       | mA       |

| Oscillator:                                                                   |          |            |            |           |          |

| Oscillator Frequency                                                          | Fosc     | 21         | 24         | 27        | kHz      |

| Percentage Frequency Change per Volt                                          | <u> </u> | -          | 0.4        | 1.0       | %/V      |

| (VDD = 10V  to  18V)                                                          | F /      |            |            |           |          |

| Sawtooth High Voltage                                                         | VOSCP    | -          | 4.0        | 4.3       | V        |

| Sawtooth Low Voltage                                                          | Voscv    | 0.7        | 1.0        | -         | V        |

| Capacitor Discharge Current                                                   | D        | 0.6        | 1.0        | 2.5       | mA       |

| Logic Inputs:                                                                 |          |            |            |           |          |

| Input Threshold Voltage                                                       | Viн      | 3.0        | 2.5        | -         | V        |

| (Pins 1, 20, 21, 22, 23, 24, 25, 26, 27)                                      | VIL      | -          | 1.6        | 1.4       | V        |

| Brake and Sensor (Pins 23, 24, 25, 26)                                        |          |            |            |           |          |

| High State Input Current ( $V_{IN} = 4V$ )                                    | Іін      | -36        | -27        | -20       | μA       |

| Low State Input Current (VIL = $0V$ )                                         | lı∟      | -50        | -40        | -30       | μA       |

| , ,                                                                           |          |            | -          |           | r ·      |

| Sequence Select, Top Driver Polarity                                          |          |            |            |           |          |

| Select, PWM Control, Brake Select,                                            |          |            |            |           |          |

| and F/R Select (Pins 1, 20, 21, 22, 27)<br>High State Input Current (Vı = 4V) | Ін       | -16        | -12        | -8        |          |

| Low State Input Current ( $VIII = 4V$ )                                       |          | -16<br>-25 | -12<br>-17 | -0<br>-10 | μΑ<br>μΑ |

|                                                                               |          | 25         |            |           | $\mu h$  |

| Enable Input Threshold Voltage (Pin 2)                                        | Viн      | 2.8        | 3.0        | 3.2       | V        |

| Hysteresis                                                                    | Vн       | 0.2        | 0.3        | 0.4       | V        |

| Enable Input Current                                                          | lin      | -          | -          | 10        | nA       |

| Overcurrent Sense Comparator:                                                 |          |            |            |           |          |

| Input Threshold Voltage                                                       | Viн      | 90         | 105        | 120       | mV       |

| Input Current                                                                 | lin      | -          | -          | 10        | nA       |

| Outputor                                                                      |          |            |            |           |          |

| Outputs:<br>Closed Loop Control Section:                                      |          |            |            |           |          |

| Tachometer Out                                                                |          |            |            |           |          |

| Output High Voltage (Isource = 1.5mA)                                         | Vон      | VR - 0.8   | VR - 0.5   | VR - 0.3  | V        |

| Output Low Voltage (Isonk = 5mA)                                              | VOL      | 0.18       | 0.27       | 0.40      | v        |

| Pulse Width                                                                   | Tw       | 95         | 105        | 115       | μs       |

| Capacitor Discharge Current (RC Terminal)                                     | lD       | 1.8        | 3          | 7.5       | mΑ       |

| Output Drivers (Pine 10, 10, 14, 15, 10, 17)                                  |          |            |            |           |          |

| Output Drivers (Pins 12, 13, 14, 15, 16, 17)<br>Sourcing 25mA                 | Vон      | 9.5        | 10.5       | 11        | V        |

| Sourcing 50mA                                                                 | Vон      | 8          | 8.8        | 9.5       | v        |

| Sinking 25mA                                                                  | VOL      | 0.6        | 1.00       | 1.6       | V        |

| Sinking 50mA                                                                  | VOL      | 1.2        | 2.0        | 3.5       | •        |

| Switching Times                                                               | TR       | 30         | 45         | 60        | ns       |

| (CL = 250pF)                                                                  | TF       | 35         | 50         | 65        | ns       |

| Switching Times                                                               | TR       | 100        | 150        | 200       | ns       |

| CL = 1000pF)                                                                  | TF       | 130        | 180        | 230       | ns       |

| Fault Output Voltage (Isink = 2mA)                                            | VFO      | -          | -          | 0.5       | V        |

| Fault Off-State Leakage                                                       | lF       | -          | 10         | -         | nA       |

| Under Voltage Lockout:                                                        |          |            |            |           |          |

| For VDD                                                                       | Vuv      | 7.0        | 8.5        | 9.9       | V        |

| Hysteresis                                                                    | VH       | 0.45       | 0.65       | 0.85      | v        |

| For VR                                                                        | VUVR     | 3.5        | 4.1        | 4.8       | V        |

| Hysteresis                                                                    | Vн       | 0.16       | 0.3        | 0.4       | V        |

| Power Supply Current                                                          |          |            |            |           |          |

|                                                                               | IDD      | -          | 2.0        | 3.0       | mA       |

| VDD = 10V                                                                     |          |            | v          | <b></b>   |          |

| VDD = 10V<br>VDD = 12V                                                        | IDD      | -          | 3.0        | 4.0       | mA       |

7560F-080718-4

determined by the RC time constant. When the capacitor discharges past the

ENABLE input switching point, the outputs will be turned off.

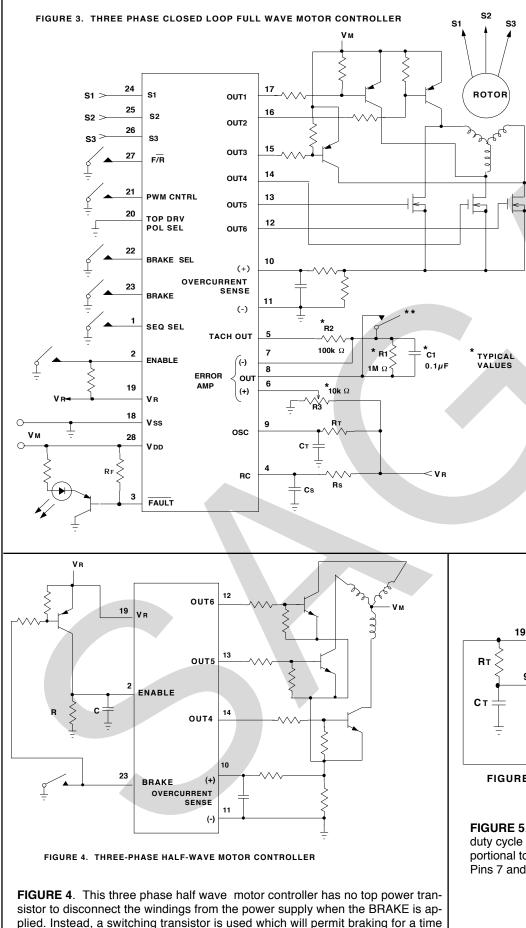

#### FIGURE 3.

The closed loop motor control operation is achieved by applying the Tachometer Output at Pin 5 into the negative terminal of the Error Amplifier (Pin 7) through an R1-C1-R2 integrating network. The R1-C1 network is configured as a feedback circuit around the amplifier. Since the Tachometer Output has a fixed positive pulse width, the average value of the pulse train is directly proportional to the motor speed. The desired speed is selected by applying a voltage at the positive input (Pin 6) of the Error Amplifier. The resultant output voltage of the Error Amplifier is applied to an internal Comparator along with a ramp waveform generated by the RC Network at Pin 9. The PWM signal at the Comparator output is used to drive outputs 1 thru 6 and complete the closed loop. For this configuration, Pin 20, the Top Driver Polarity Select must be tied to Ground.

\*\* Switch used to connect the error amplifier out and (-) input together when Brake Select input is low and Brake is applied. The speed setting selected by R3 also sets the PWM rate during braking.

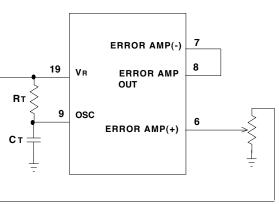

FIGURE 5. OPEN LOOP CONTROLLER

**FIGURE 5**. In this configuration, the PWM output duty cycle to the motor drivers is directly proportional to the DC voltage applied to Pin 6, since Pins 7 and 8 are tied together.

current during braking can be controlled.

## TABLE 1. OUTPUT COMMUTATION SEQUENCE FOR THREE-PHASE OPERATION

|                                                                                                                                                                                                                             |                                    |                   | LS756       | 0F          |                                                          |                                                                       |             |                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------|-------------|----------------------------------------------------------|-----------------------------------------------------------------------|-------------|-----------------------|

|                                                                                                                                                                                                                             | CTRICAL<br>120°<br>, <b>S2, S3</b> | F/R EN            | BRK         | ocs         | TOP<br>DRIVERS<br><b>01, 02, 03</b>                      | BOTTOM<br>DRIVERS<br><b>04, 05, 06</b>                                | FAULT       |                       |

| $\begin{array}{cccc} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 1 \end{array}$                                                                                                                                                            | 0 1<br>0 1                         | 1 1<br>1 1        | 0<br>0      | 0<br>0      | $\begin{array}{cccc} 0 & 1 & 1 \\ 1 & 1 & 0 \end{array}$ | 0 1 0<br>0 1 0                                                        | 1<br>1      |                       |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                        | 0 0<br>1 0                         | 1 1<br>1 1        | 0<br>0      | 0<br>0      | $\begin{array}{ccc}1&1&0\\1&0&1\end{array}$              | 1 0 0<br>1 0 0                                                        | 1<br>1      |                       |

| 0 1 1 0<br>0 0 1 0                                                                                                                                                                                                          | 1 0<br>1 1                         | 1 1<br>1 1        | 0<br>0      | 0<br>0      | $\begin{array}{ccc}1&0&1\\0&1&1\end{array}$              | 0 0 1<br>0 0 1                                                        | 1           | <b>EN</b> = ENABLE    |

| $\begin{array}{cccc} 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 \end{array}$                                                                                                                                                            | 0 0<br>1 1                         | x x<br>x x        | 0<br>0      | x<br>x      | $\begin{array}{cccc}1&1&1\\1&1&1\end{array}$             | 0 0 0<br>0 0 0                                                        | 0<br>0      | <b>BRK</b> = BRAKE    |

| 0 0 0 0 1 0 1                                                                                                                                                                                                               | 0 1 0 1                            | 0 1 0 1           | 0<br>0      | 0<br>0      | 1 0 1<br>1 0 1                                           | 1 0 0<br>0 0 1                                                        | 1           | OCS = OVER<br>CURRENT |

| 1 1 0 1<br>1 1 1 1                                                                                                                                                                                                          | 0 0 1 0                            | 0 1               | 0<br>0      | 0           | 0 1 1<br>0 1 1                                           | 0 0 1 0                                                               | 1           | SENSE                 |

| 0 1 1 0 0 1 0                                                                                                                                                                                                               | 1 0 1 1                            | 0 1<br>0 1        | 0<br>0      | 0<br>0      | 1 1 0 1 1 0                                              | 0 1 0 1 0                                                             | 1           |                       |

| 0 1 0 0<br>1 0 1 1<br>x x x x                                                                                                                                                                                               | 0 0<br>1 1<br>x x                  | X X<br>X X<br>X X | 0<br>0<br>1 | x<br>x      |                                                          | $\begin{array}{cccc} 0 & 0 & 0 \\ 0 & 0 & 0 \\ 1 & 1 & 1 \end{array}$ | 0<br>0<br>1 |                       |

| x x x x                                                                                                                                                                                                                     |                                    | x x<br>x 0        | 0           | x<br>1<br>x |                                                          |                                                                       | 0           |                       |

| NOTE 1: This Table assumes the Top Driver Polarity Select (Pin 20) = Logic 0.<br>For Pin 20 = Logic 1, invert the polarity of the top drivers.                                                                              |                                    |                   |             |             |                                                          |                                                                       |             |                       |

| <b>NOTE 2</b> : For the LS7561F, the Overcurrent Sense = Logic 1 only forces the bottom drivers to a Logic 0.<br>It has no effect on the top driver outputs which are determined by the other inputs as shown in the table. |                                    |                   |             |             |                                                          |                                                                       |             |                       |

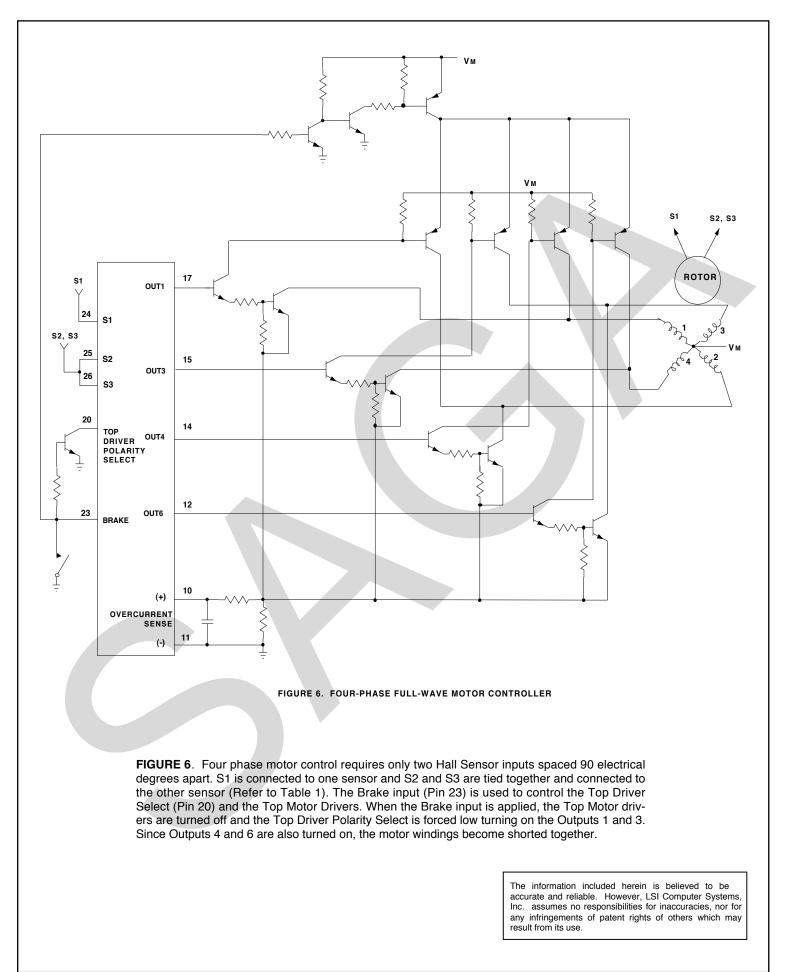

# TABLE 2. OUTPUT COMMUTATION SEQUENCE FOR FOUR-PHASE OPERATION LS7560F

|   | OR ELECT<br>RATION =<br><b>S2, S3</b> | - | EN | BRK | ocs | TOP<br>DRIVERS<br><b>01, 03</b> | BOTTOM<br>DRIVERS<br><b>04, 06</b> |   |                    |

|---|---------------------------------------|---|----|-----|-----|---------------------------------|------------------------------------|---|--------------------|

|   |                                       |   |    |     |     | ,                               | ,                                  |   |                    |

| 0 | 0                                     | 1 | 1  | 0   | 0   | 1 0                             | 0 0                                | 1 | EN = ENABLE        |

| 1 | 0                                     | 1 | 1  | 0   | 0   | 0 1                             | 0 0                                | 1 |                    |

| 1 | 1                                     | 1 | 1  | 0   | 0   | 0 0                             | 1 0                                | 1 | <b>BRK</b> = BRAKE |

| 0 | 1                                     | 1 | 1  | 0   | 0   | 0 0                             | 01                                 | 1 |                    |

| 0 | 0                                     | 0 | 1  | 0   | 0   | 0 0                             | 1 0                                | 1 | OCS = OVER         |

| 1 | 0                                     | 0 | 1  | 0   | 0   | 0 0                             | 01                                 | 1 | CURRENT            |

| 1 | 1                                     | 0 | 1  | 0   | 0   | 1 0                             | 0 0                                | 1 | SENSE              |

| 0 | 1                                     | 0 | 1  | 0   | 0   | 0 1                             | 0 0                                | 1 | GENGE              |

| х | х                                     | х | x  | 1   | х   | 0 0                             | 1 1                                | 1 |                    |

| х | х                                     | X | X  | 0   | 1   | 0 0                             | 0 0                                | 0 |                    |

| х | x                                     | х | 0  | 0   | х   | 0 0                             | 0 0                                | 0 |                    |

**NOTE 1**: Sequence Input (Pin 1) set at a Logic 1.

**NOTE 2**: This Table assumes the Top Driver Polarity Select (Pin 20) = Logic 1. For Pin 20 = Logic 0, invert the polarity of the top drivers.

**NOTE 3**: For the LS7561F, the Overcurrent Sense = Logic 1 only forces the bottom drivers to a Logic 0. It has no effect on the Top Driver Outputs which are determined by the other inputs as shown on the table.